La demanda de SSD cada vez más grandes y rápidos no se detiene. En el panorama actual, SK Hynix ha presentado una propuesta basada en una NAND flash de 5 bits por celda que utiliza una arquitectura denominada split-cell. Según la compañía, esta combinación podría aumentar la capacidad y la velocidad de los SSD, además de extender la durabilidad, sin incrementar los costos de producción. En este artículo analizamos qué significa esta innovación y qué impacto podría tener para el almacenamiento moderno.

Qué es split-cell 5-bit NAND

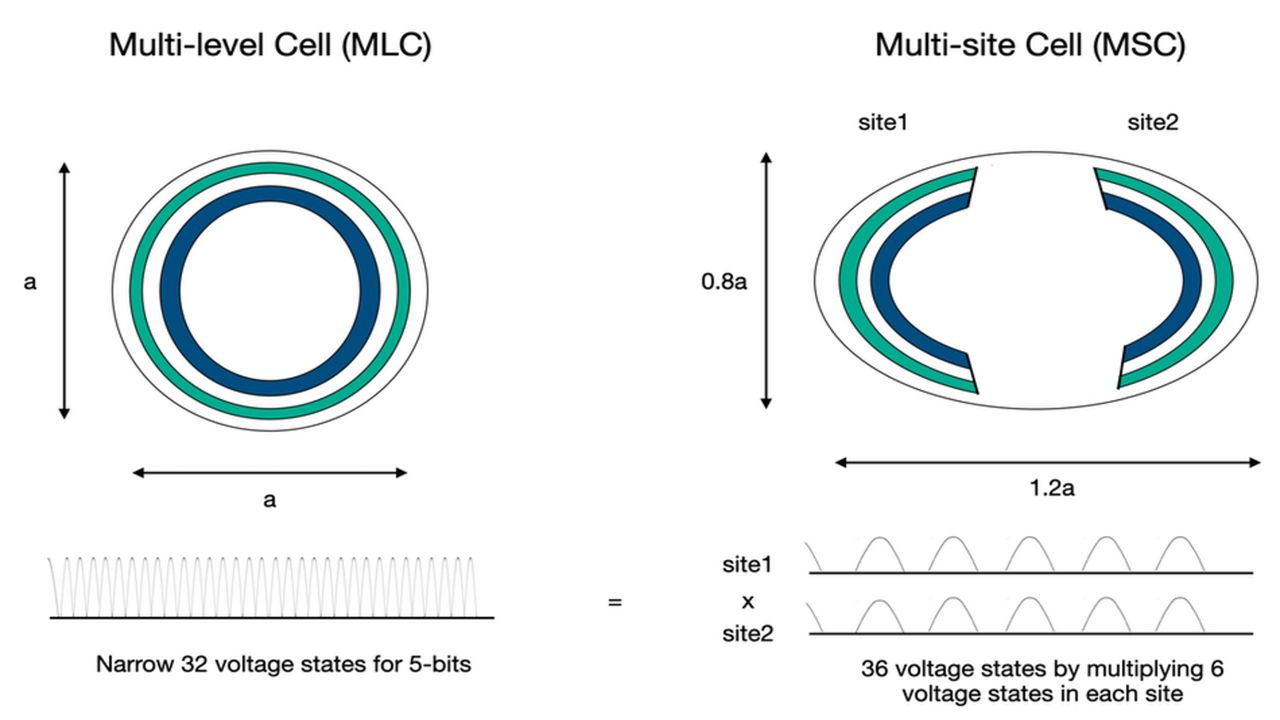

En términos prácticos, split-cell se refiere a dividir cada celda de memoria en subceldas que pueden gestionarse de forma más independiente durante la programación y la lectura. Al combinar una celda de 5 bits por celda —es decir, 32 niveles— con esta división, la arquitectura busca reducir interferencias entre celdas, optimizar la retención de datos y distribuir de manera más uniforme el desgaste. SK Hynix afirma que este enfoque aprovecha mejor la topología de la celda y las rutas de lectura/escritura para lograr mayores densidades sin costos de proceso adicionales.

Beneficios clave

– Capacidad: mayor densidad por paquete de NAND al soportar 5 bits por celda con una gestión de subceldas que optimiza el uso del área útil.

– Velocidad: paralelismo entre subceldas y mejoras en lectura y sensado permiten incrementar las tasas de transferencia y reducir la latencia en operaciones críticas.

– Durabilidad: distribución más uniforme del desgaste y reducción de errores relacionados con el desgaste, lo que contribuye a una vida útil más larga del SSD.

– Costos: la casa matriz sostiene que no es necesario un aumento de costos, apoyando la idea de que las mejoras en rendimiento y densidad pueden compensar el gasto de implementación gracias a rendimientos de fabricación superiores.

Implicaciones para el mercado

La promesa de mayores SSD sin subir costos podría afectar tanto a centros de datos como a soluciones de consumo. En entornos de nube y analítica, las ventajas de mayor capacidad y rendimiento podrían traducirse en menores costos por terabyte y mejor eficiencia operativa. Para los fabricantes de controladores y firmware, surge la necesidad de adaptar software y algoritmos de gestión de memoria para aprovechar plenamente el split-cell y los 32 niveles de la celda.

Desafíos y consideraciones

Aunque la propuesta es atractiva, existen desafíos técnicos y de mercado. Se requieren controladores y firmware compatibles que gestionen de forma eficiente 32 niveles por celda. Además, es necesario validar a largo plazo la fiabilidad de la lectura/escritura en condiciones extremas de temperatura y carga sostenida, así como asegurar una profundidad de calibración adecuada para mantener consistencia entre lotes. También hay que evaluar la complejidad de la fabricación y las posibles implicaciones en la cadena de suministro y el costo total de propiedad.

Conclusión

La introducción de una NAND flash de 5 bits por celda con arquitectura split-cell representa una propuesta relevante para aumentar la capacidad y el rendimiento de los SSD sin incurrir en costos adicionales, según SK Hynix. Si la tecnología se consolida y se traduce en productos comerciales, podría marcar un hito en la evolución de la memoria flash para almacenamiento de alto rendimiento y alta densidad. Aún queda por ver cómo se traducen estas promesas en disponibilidad para fabricantes, integradores y usuarios finales.

from Latest from TechRadar https://ift.tt/B6EhwXY

via IFTTT IA